Two new blocks and demonstrations have been prepared.

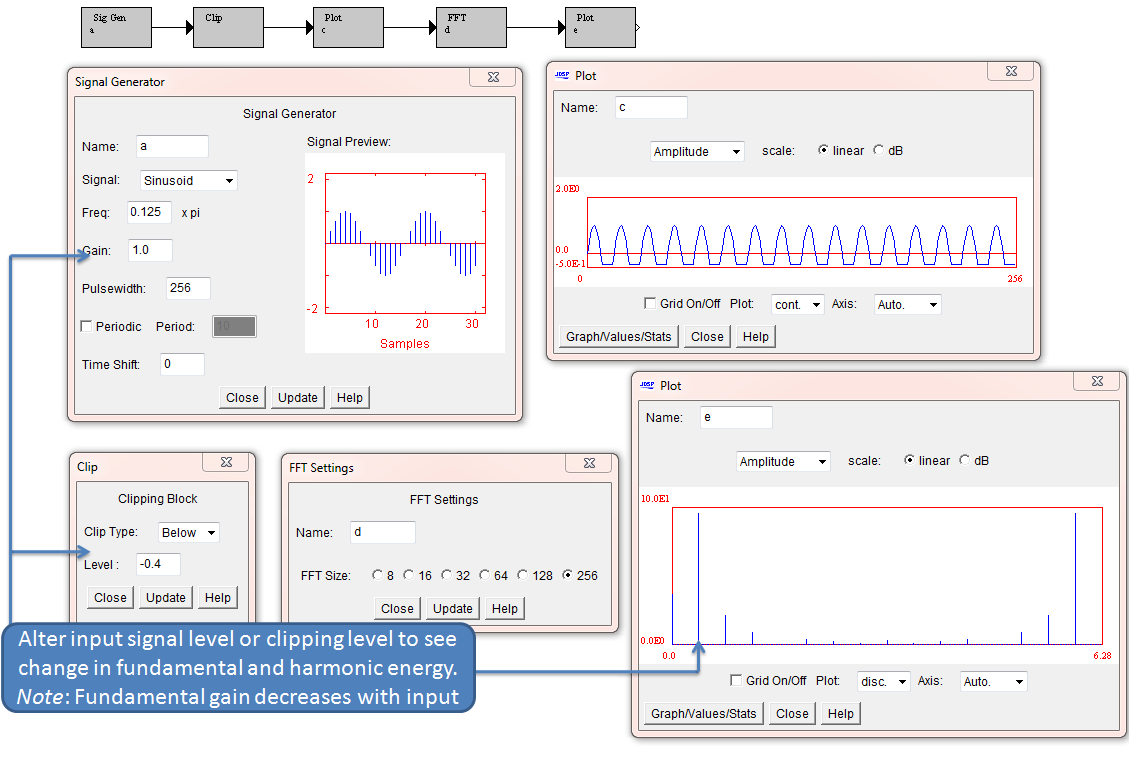

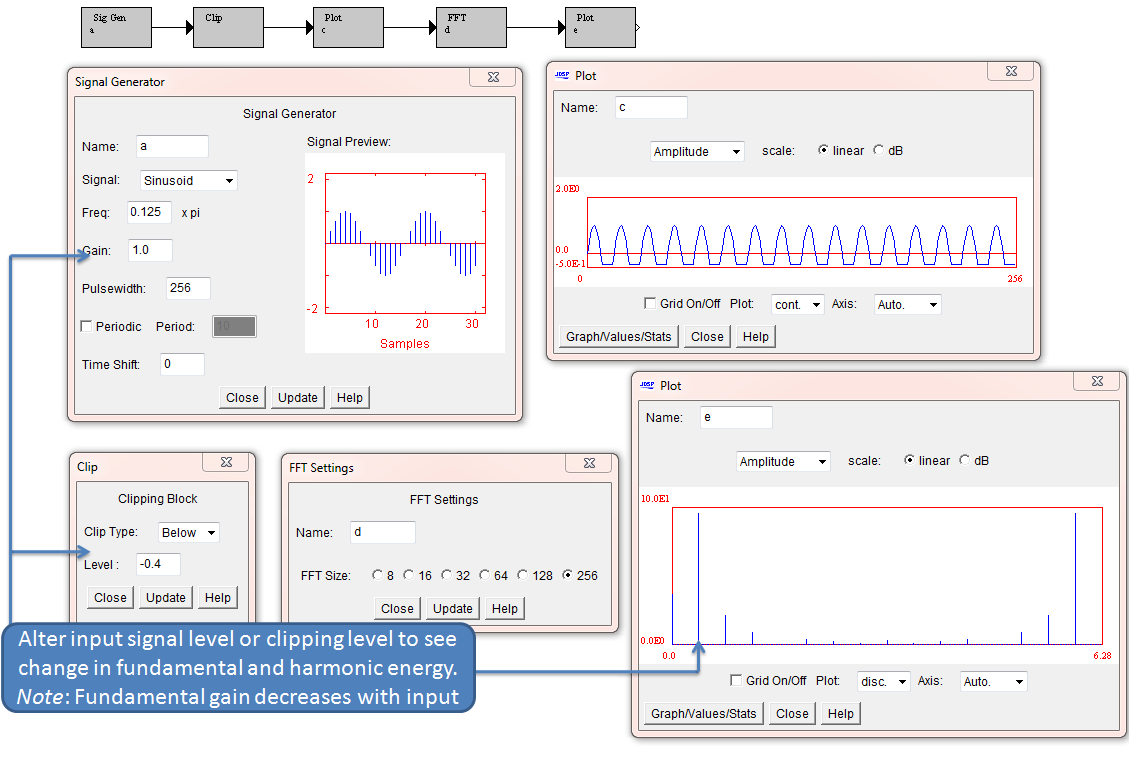

The first of these new blocks and demonstrations has been created to

demonstrate an impairment inherent to achieving efficient high-power

operation in a power amplifier. This demonstration is geared towards

wireless applications, though it is equally relevant to both wireless and

wireline communications. The demonstration illustrates the effect of

an amplifier's variable gain when it operates in its gain compression region, where

clipping occurs but high efficiency is attained. The demonstration was

presented at an ASEE conference and has been documented, and a training

video has been prepared here.

|

Figure 1.

JDSP Demonstration of RF Amplifier Clipping and Gain Compression |

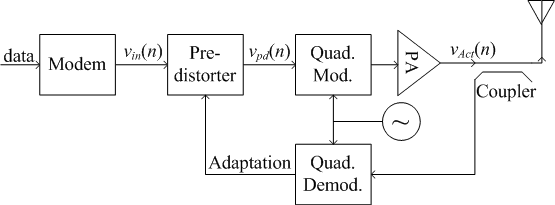

The second demonstration simulates the correction of

amplifier distortion utilizing the gain-based look-up-table predistortion

algorithm developed by James Cavers [1]. In this algorithm, a local

receiver is used to measure the output transmitted from the power amplifier.

This output is then aligned, and compared to the point the baseband DSP

desired to transmit. Where it is not the desired point, a set of

complex gain correction factors is developed.

|

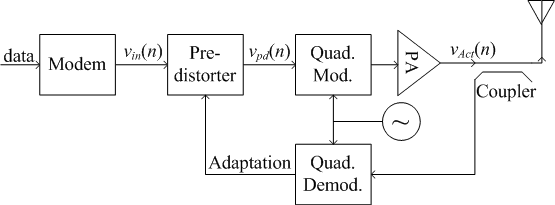

Figure 2. Typical

Digital Predistortion Topology. |

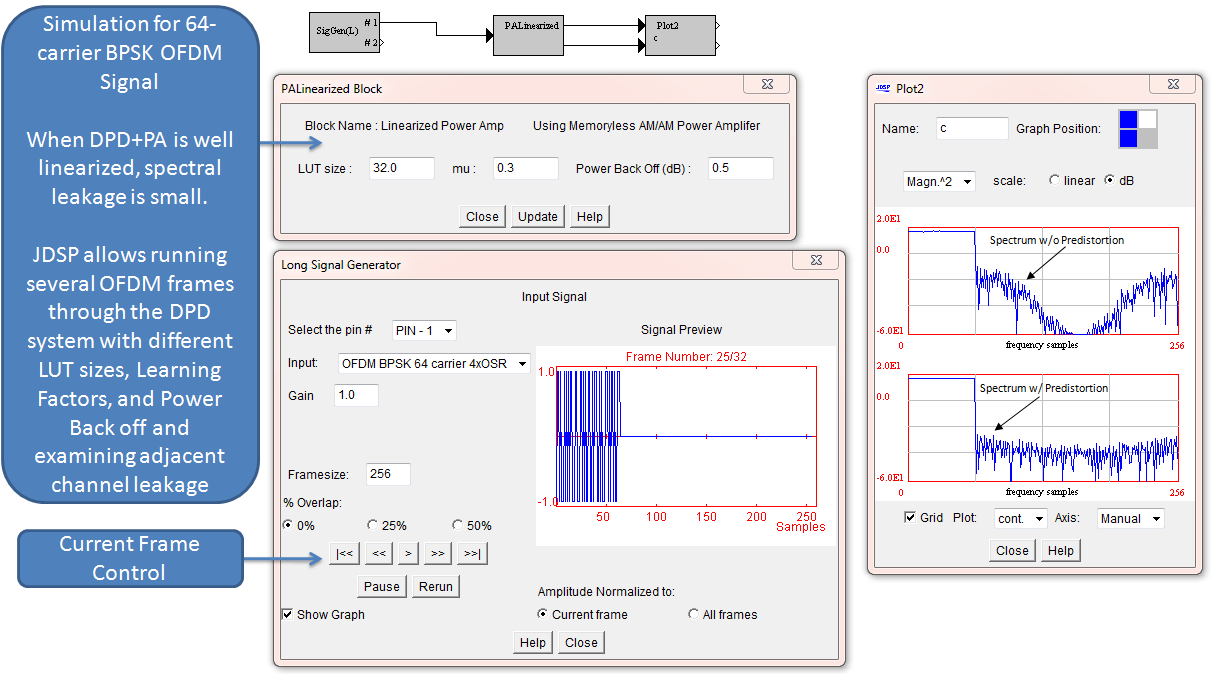

The digital predistortion algorithm assumes that the

amplifier gain compression is strictly a function of the amplifier's input

signal power. The algorithm groups input power into bins of a specific

range. These bins are allocated based linearly on input power.

When a point for a given bin is driven by the DSP, the value from the PA

output measured by the receiver is compared to the driven value. A

least-mean-squares algorithm is used to determine the required correction

factor. This correction factor is then applied at the output of the

DSP to distort the signal prior to the amplifier (or pre-distort) it, such

that when the amplifier introduces its distortion the gain achieves the

desired value. As the amplifier has a gain compressive characteristic

for increasing input powers, the predistorter typically has a gain-expansive

characteristic. A J-DSP demonstration of this was prepared and

demonstrated at ASEE. A video tutorial of the demonstration is

available here.

|

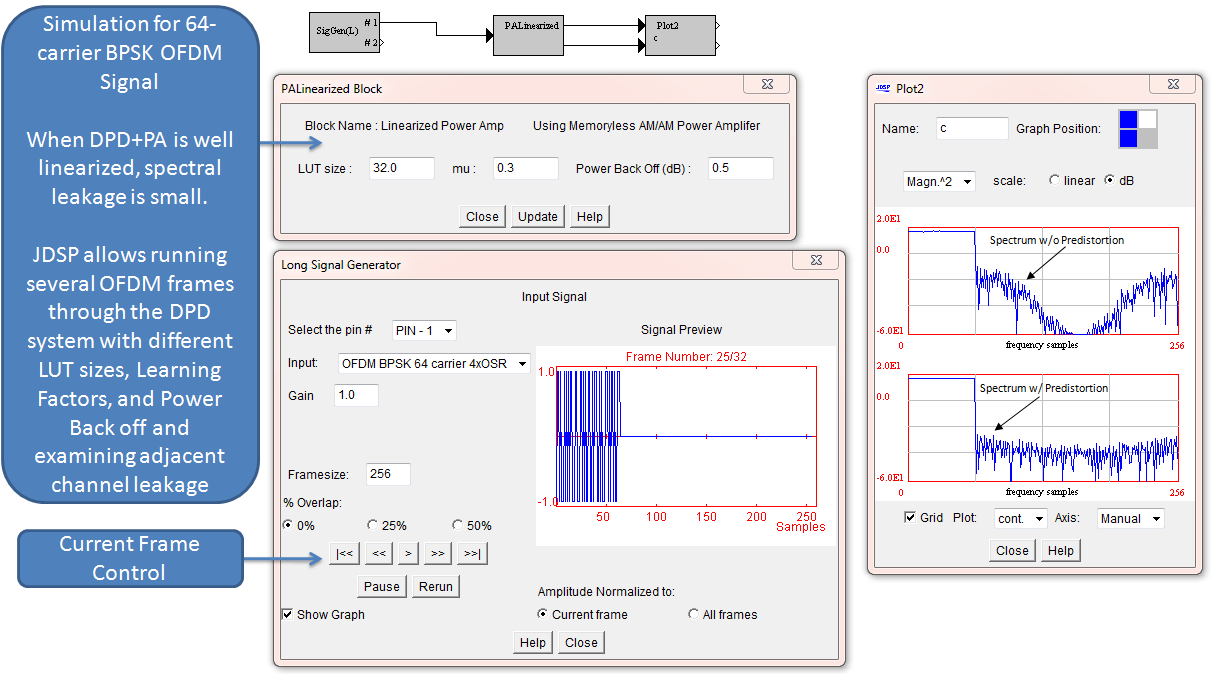

Figure 3.

J-DSP Digital Predistortion Demonstration |

J-DSP Executable:

Click here to access the Power Amplifier JDSP demonstration

platform. (EEE407,EEE455)

Publications:

A. Spanias, R. Santucci, T. Gupta, M. Shah, "Advanced

Functions of Java-DSP For Use in Electrical Engineering and Computer

Engineering Courses",

Proceedings of ASEE, June 2010.

Related Publications:

Santucci, R., Spanias, A., "A

Block Adaptive Predistortion Algorithm for Transceivers with Long

Transmit-Receive Latency," Communications, Control and Signal Processing

(ISCCSP), 2010 4th International Symposium on, pp.1-6, 3-5 March 2010.

Presentations:

Click here for the Power Point slides for ASEE 2010 presentation.

Click here for the Power Point slides for the EEE407 JDSP PA presentation

Click here for the Power Point slides for the EEE455 JDSP PA presentation

Video Tutorials:

J-DSP Amplifier Clipping Video

Tutorial (9MByte WMV file)

J-DSP Digital

Predistortion Video Tutorial (6MByte WMV file)

ASEE2011 Presentation (PowerPoint 2007)

This work is sponsored by the NSF Phase 3 grant

award 0817596 (DWS 0380).